GTKWave

| Dernière version | 3.3.98 () |

|---|---|

| Dépôt | svn.code.sf.net/p/gtkwave/code |

| Écrit en | C |

| Interface | GTK |

| Système d'exploitation | Type Unix |

| Formats lus | GTKWave Saved session (deprecated) (d) et GTKWave Saved session (d) |

| Formats écrits | GTKWave Saved session (deprecated) (d) et GTKWave Saved session (d) |

| Type | Science |

| Licence | Licence publique générale GNU |

| Site web | gtkwave.sourceforge.net |

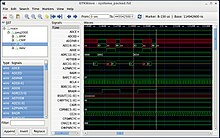

GTKWave est un logiciel libre de visualisation de forme d'onde et de chronogramme multiplate-forme pour Unix, Win32, et Mac OSX, il supporte notamment les fichiers de log au format LXT, LXT2, VZT, FST, et GHW, ainsi que les fichiers standards de Verilog VCD et EVCD[1].

Génération modifier

Il est possible de générer des fichiers au format spécifique à GTKWave, .gtkw depuis le langage Python à l'aide de la bibliothèque nmutil[2].

GPIO modifier

l'outil pispy permet de capturer les états des GPIO et d'invoquer directement GTKWave pour les analyser[3].

FPGA modifier

Les outils deux principaux logiciels de langage de description de matériel Verilog et langage de vérification de matériel associé, que sont Icarus Verilog (en) et Verilator permettent de faire des sortie pour GTKWave[4],[5],[6]. Il peut également être utilisé avec le langage VHDL via l'outil GHDL[7],[8],[9]. Le langage de description Migen en Python permet également de l'utiliser[10].

Le module Python Wavedisp, permet la conversion entre les formats Tcl propriétaires ModelSim (Mentor) et RivieraPro (Aldec) et les formats GTKWave[11].

Le projet de SoC sous licence libre, Libre-SoC, à également choisi de l'utiliser pour visualiser la sortie de l'intégration continue (CI) de son développement et à fait une présentation à ce sujet au FOSDEM[12].

Notes et références modifier

- (en) « Welcome to GTKWave », sur GTKWave

- (en) « GTKWave Tutorial », sur LibreSOC

- Gay 2015, p. 95.

- (en) « 3rd Party Tools - GTKWave », sur Icarus Verilog (en)

- (en) « Simulator Support », sur docs.cocotb.org

- (en) « Taking a New Look at Verilator », sur ZipCPU,

- V. Angelov, Simulations with VHDL, Institut de physique de l'Université de Heidelberg, (lire en ligne)

- Thibaut Cuvelier, « Introduction au langage VHDL », sur Developpez.com,

- « Simulation VHDL », sur doc.ubuntu-fr.org

- (en) Brian Benchoff, « Designing Flip-Flops With Python and Migen », sur Hackaday,

- Christophe Clienti, « Simplifier la visualisation de chronogrammes », sur Linuxfr,

- (en) « gtkwave tutorial », sur libre-soc.org

Bibliographie modifier

- (en) Guru Prasad, Verilog Program Examples using iverilog and GTKwave, Manipal, Manipal Institute of Technology, (DOI 10.13140/RG.2.2.30515.55840/1)

- (zh) 韩改宁, 许青林 et 段群, « 基于iverilog和GTKWave在硬件逻辑设计中的应用研究 (Research and Application of Digital Circuit Base on Iverilog and GTKWave) », 《咸阳师范学院学报》, Xianyang, 咸阳师范学院信息工程学院 (School of Information Engineering,Xianyang Normal University), no 4, , p. 52-54 (présentation en ligne) (présentation en anglais)

- Warren Gay, chap. 9 « PiSpy », dans Exploring the Raspberry Pi 2 with C++, , 95–103 p. (DOI 10.1007/978-1-4842-1739-9_9)

- (en) Geeta Yadav et Neeraj Kr. Shukla, « Pre-Eminance of Open Source Eda Tools and Its Types in The Arena of Commercial Electronics », International Journal of Advanced Computer Science and Applications, vol. 4, no 12, (DOI 10.14569/IJACSA.2013.041225)

- (en) Payal Yadav et Asma Fathima, « VLSI Implementation of Gold Sequence by Novel Method », International Journal of Advanced Studies in Computer Science and Engineering (IJASCSE), vol. 2, no 2, , p. 32-38 (ISSN 2278-7917, lire en ligne)

- N. Ait Said, M. Benabdenbi et G. Villanova Magalhães, « Prototypage Matériel-Logiciel de Systèmes Intégrés avec l'architecture RISC-V », J3eA, Univ. Grenoble Alpes, CNRS, Grenoble INP (Institute of Engineering Univ. Grenoble Alpes), TIMA, vol. 19, no Hors série 1, (DOI doi.org/10.1051/j3ea/20191016, présentation en ligne, lire en ligne)

- S. Jovanovic et S. Weber, « Modélisation SystemC-TLM de systèmes à base de processeur », J3eA, Institut Jean Lamour (UMR7198) et Pôle CNFM MIGREST – Nancy, Université de Lorraine, vol. 18, no Hors série 1, (DOI 10.1051/j3ea/20191009, présentation en ligne, lire en ligne)

- (en) Guru Prasad, « A Tutorial on Design of Datapath and Controller of an ALU using Verilog and Verification using Open Source EDA Tools », dans 2021 2nd International Conference on Communication, Computing and Industry 4.0 (C2I4), IEEE, (ISBN 978-1-6654-2014-3, DOI 10.1109/C2I454156.2021.9689339)

- (en) R Ilaiyaraja et S. Sedhumadhavan, « Design & Performance Analysis of Area Optimized in BPSK on NCO and High Speed 64 Bit-QAM with Gardner Algorithm », dans 2018 Second International Conference on Inventive Communication and Computational Technologies (ICICCT) (DOI 10.1109/ICICCT.2018.8473312, présentation en ligne)

- (en) GTKWave User Guide, Renesas, (lire en ligne)

- (hr) Danica Majić, Prikaz rezultata Verilog simulacije u LaTeX dokumentu, (présentation en ligne)

Site officiel modifier

(en) Site officiel